## INTELLIGENT DYNAMIC CLOCK SWITCH PLL CLOCK DRIVER

MARCH 2005 REV. P1.0.1

## **GENERAL DESCRIPTION**

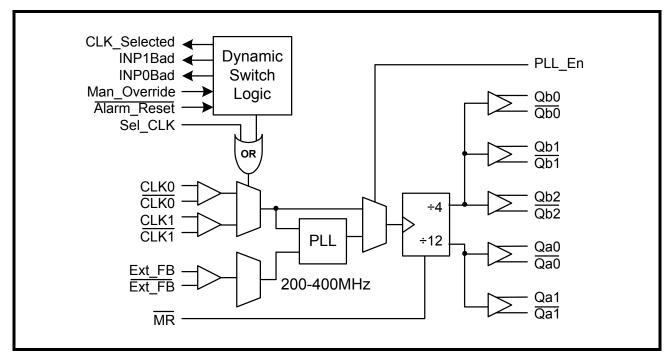

The XRK7933 is a PLL clock driver designed specifically for redundant clock tree designs. The device receives two differential LVPECL clock signals from which it generates 5 new differential LVPECL clock outputs. Two of the output pairs regenerate the input signals frequency and phase while the other three pairs generate 3x, phase aligned clock outputs. External PLL feedback is used to also provide zero delay buffer performance.

The XRK7933 Intelligent Dynamic Clock Switch circuit continuously monitors both input CLK signals. Upon detection of a failure (CLK stuck HIGH or LOW for at least 1 period), the INP BAD for that CLK will

be latched (H). If that CLK is the primary clock, the device will switch to the good secondary clock and phase/frequency alignment will occur with minimal output phase disturbance. The typical phase bump caused by a failed clock is eliminated.

## **FEATURES**

- Fully Integrated PLL

- Intelligent Dynamic Clock Switch

- LVPECL Clock Outputs

- LVCMOS Control I/O

- 3.3V Operation

- 32-Lead LQFP Packaging

FIGURE 1. BLOCK DIAGRAM OF THE XRK7933

XRK7933

## PRODUCT ORDERING INFORMATION

| PRODUCT NUMBER | PACKAGE TYPE | OPERATING TEMPERATURE RANGE |

|----------------|--------------|-----------------------------|

| XRK7933        | 32-Lead LQFP | -40°C to +85°C              |

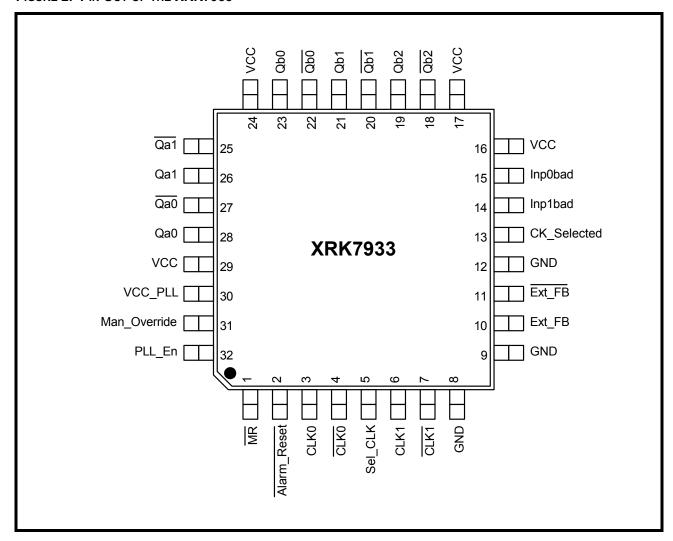

FIGURE 2. PIN OUT OF THE XRK7933

## **PIN DESCRIPTIONS**

| PIN NAME                 | Түре                         | DESCRIPTION                                                                                                                                                                  |

|--------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK0, CLK0<br>CLK1, CLK1 | LVPECL Input<br>LVPECL Input | Differential PLL clock reference (CLK0 pulldown, CLK0 pullup)  Differential PLL clock reference (CLK1 pulldown, CLK1 pullup)                                                 |

| Ext_FB, Ext_FB           | LVPECL Input                 | Differential PLL feedback clock (Ext_FB pulldown, Ext_FB pullup)                                                                                                             |

| Qa[1:0], Qa[1:0]         | LVPECL Output                | Differential 1x output pairs                                                                                                                                                 |

| Qb[2:0], Qb[2:0]         | LVPECL Output                | Differential 3x output pairs                                                                                                                                                 |

| Inp0bad                  | LVCMOS Output                | Indicates detection of a bad input reference clock 0 with respect to the feed-back signal. The output is active HIGH and will remain HIGH until the alarm reset is asserted. |

| Inp1bad                  | LVCMOS Output                | Indicates detection of a bad input reference clock 1 with respect to the feed-back signal. The output is active HIGH and will remain HIGH until the alarm reset is asserted. |

| Clk_Selected             | LVCMOS Output                | 0 - if clock 0 is selected 1 - if clock 1 is selected                                                                                                                        |

| Alarm_Reset              | LVCMOS Input                 | 0 - will reset the input bad flags and align Clk_Selected with Sel_Clk. The input is one-shotted (50K $\Omega$ pullup).                                                      |

| Sel_Clk                  | LVCMOS Input                 | 0 - selects CLK0<br>1 - selects CLK1 (40kΩ pulldown)                                                                                                                         |

| Manual_Override          | LVCMOS Input                 | 1 - disables internal clock switch circuitry (40KΩ pulldown).                                                                                                                |

| PLL_En                   | LVCMOS Input                 | 0 - bypasses selected input reference around the phase-locked loop (50K $\!\Omega$ pullup).                                                                                  |

| MR                       | LVCMOS Input                 | $0$ - resets the internal dividers forcing Q outputs LOW. Asynchronous to the clock (50K $\!\Omega$ pullup).                                                                 |

| VCCA                     | Power Supply                 | PLL power supply                                                                                                                                                             |

| VCC                      | Power Supply                 | Digital power supply                                                                                                                                                         |

| GNDA                     | Power Supply                 | PLL Ground                                                                                                                                                                   |

| GND                      | Power Supply                 | Digital Ground                                                                                                                                                               |

## **ABSOLUTE MAXIMUM RATINGS**<sup>a</sup>

| SYMBOL           | CHARACTERISTICS     | MIN  | MAX                  | Unit | CONDITION |

|------------------|---------------------|------|----------------------|------|-----------|

| $V_{CC}$         | Supply Voltage      | -0.3 | 3.6                  | V    |           |

| V <sub>IN</sub>  | DC Input Voltage    | -0.3 | V <sub>CC</sub> +0.3 | V    |           |

| V <sub>OUT</sub> | DC Output Voltage   | -0.3 | V <sub>CC</sub> +0.3 | V    |           |

| I <sub>IN</sub>  | DC Input Current    |      | <u>+</u> 20          | mA   |           |

| I <sub>OUT</sub> | DC Output Current   |      | <u>+</u> 50          | mA   |           |

| T <sub>S</sub>   | Storage Temperature | -65  | 125                  | °C   |           |

**a.** Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

## **GENERAL SPECIFICATIONS**

| SYMBOL          | CHARACTERISTICS                                                                                                  | Min  | Түр                | Max          | Unit | Condition          |

|-----------------|------------------------------------------------------------------------------------------------------------------|------|--------------------|--------------|------|--------------------|

| V <sub>TT</sub> | Output termination voltage                                                                                       |      | V <sub>CC</sub> -2 |              | V    |                    |

| MM              | ESD Protection (Machine model)                                                                                   | 200  |                    |              | V    |                    |

| НВМ             | ESD Protection (Human body model)                                                                                | 2000 |                    |              | V    |                    |

| LU              | Latch-up immunity                                                                                                | 200  |                    |              | mA   |                    |

| C <sub>IN</sub> | Input Capacitance                                                                                                |      | 4.0                |              | pF   | Inputs             |

| $\theta_{JA}$   | Thermal resistance junction to ambient JESD 51-3, single layer test board  JESD 51-6, 2S2P multilayer test board |      |                    | 62.0<br>47.0 | °C/W | Natural convection |

| θJC             | Thermal resistance junction to case                                                                              |      |                    | 14           | °C/W |                    |

|                 | Operating junction temperature                                                                                   |      |                    | 115          | °C   |                    |

# DC Characteristics ( $V_{CC}$ = 3.3 $\pm$ 5%, $T_A$ = -40°C to +85°C)

| SYMBOL                                                                 | CHARACTERISTICS                             | Min                  | TYP | MAX                   | Unit | Condition                                                |  |

|------------------------------------------------------------------------|---------------------------------------------|----------------------|-----|-----------------------|------|----------------------------------------------------------|--|

| LVCMOS control inputs (MR, PLL_En, Sel_CLK, Man_Override, Alarm_Reset) |                                             |                      |     |                       |      |                                                          |  |

| V <sub>IH</sub>                                                        | Input voltage high                          | 2.0                  |     | VCC+0.3               | V    |                                                          |  |

| V <sub>IL</sub>                                                        | Input voltage low                           |                      |     | 0.8                   | V    |                                                          |  |

| I <sub>IN</sub>                                                        | Input current <sup>a</sup>                  | 100                  |     | -150                  | μΑ   | V <sub>IN</sub> =V <sub>CC</sub> or V <sub>IN</sub> =GND |  |

| LVCMOS                                                                 | Control Outputs                             |                      |     |                       |      |                                                          |  |

| V <sub>OH</sub>                                                        | Output High Voltage                         | 2.0                  |     |                       | V    | I <sub>OH</sub> =-10mA                                   |  |

| V <sub>OL</sub>                                                        | Output Low Voltage                          |                      |     | 0.55                  | ٧    | I <sub>OL</sub> =10mA                                    |  |

| LVPECL o                                                               | LVPECL clock inputs (CLK, CLK) <sup>b</sup> |                      |     |                       |      |                                                          |  |

| I <sub>IN</sub>                                                        | Input current                               |                      |     | <u>+</u> 100          | μΑ   | $V_{IN} = V_{CC}$ or $V_{IN} = GND$                      |  |

| LVPECL o                                                               | lock outputs (Qa[1:0],                      | [2:0])               |     |                       |      |                                                          |  |

| V <sub>OH</sub>                                                        | Output high voltage                         | V <sub>CC</sub> -1.2 |     | V <sub>CC</sub> -0.7  | V    | Termination $50\Omega$ to $V_{TT}$                       |  |

| V <sub>OL</sub>                                                        | Output low voltage                          | V <sub>CC</sub> -1.9 |     | V <sub>CC</sub> -1.45 | ٧    | Termination $50\Omega$ to $V_{TT}$                       |  |

| Supply Co                                                              | Supply Current                              |                      |     |                       |      |                                                          |  |

| I <sub>GND</sub>                                                       | Maximum ground supply current - gnd pins    |                      |     | 180                   | mA   | GND pins                                                 |  |

| I <sub>CCPLL</sub>                                                     | Maximum PLL power supply - VCC_PLL pin      |                      |     | 15                    | mA   | V <sub>CCPLL</sub> pin                                   |  |

- **a.** Inputs have internal pullup/pulldown resistors which affect the input current.

- **b.** Clock inputs driven by LVPECL compatible signals.

## INTELLIGENT DYNAMIC CLOCK SWITCH PLL CLOCK DRIVER

## AC CHARACTERISTICS ( $V_{CC}$ = 3.3 $\pm$ 5%, $T_A$ = -40°C to +85°C) (Note 5)

| SYMBOL                         | PARAMETER                                      | Min                  | Түр | Max                  | Unit     | CONDITION                   |

|--------------------------------|------------------------------------------------|----------------------|-----|----------------------|----------|-----------------------------|

| f <sub>ref</sub>               | Input Reference Frequency ÷12 feedback         | 16.67                |     | 33.3                 | MHz      | Locked                      |

| f <sub>VCO</sub>               | PLL VCO Lock Range                             | 200                  |     | 400                  | MHz      | Qa Output used for feedback |

| f <sub>MAX</sub>               | Output Frequency                               |                      |     |                      | MHz      |                             |

|                                | Qa[1:0]                                        | 16.67                |     | 33.3                 |          |                             |

|                                | Qa[1:0]                                        | 50                   |     | 100                  |          |                             |

| f <sub>refDC</sub>             | Reference Input Duty Cycle                     | 25                   |     | 75                   | %        |                             |

| $t_{pd}$                       | Propagation Delay                              |                      |     |                      |          |                             |

|                                | CLKn to Ext_FB (SPO) <sup>c</sup>              | -150                 |     | 150                  | ps       | PLL_EN = 1                  |

|                                | CLKn to Q (Bypass)                             |                      |     | 5                    | ns       | PLL_EN = 0                  |

| V <sub>PP</sub>                | Differential input voltage (peak-to-peak)      | 0.25                 |     | 1.3                  | V        |                             |

| V <sub>CMR</sub>               | Differential input crosspoint voltage          | V <sub>CC</sub> -1.7 |     | V <sub>CC</sub> -0.3 | V        |                             |

| t <sub>skew</sub>              | Output Skew                                    |                      |     |                      |          |                             |

|                                | Within Qa[1:0] or Qb[2:0]                      |                      |     | 50                   | ps       |                             |

|                                | All outputs                                    |                      |     | 80                   | ps       |                             |

| $\Delta_{ m per/cycle}$        | Rate of change of periods                      |                      |     |                      |          |                             |

|                                | Qa[1:0] <sup>d</sup>                           |                      |     | 50                   | ps/cycle |                             |

|                                | Qb[2:0] <sup>d</sup>                           |                      |     | 25                   |          |                             |

|                                | Qa[1:0] <sup>e</sup>                           |                      |     | 400                  |          |                             |

|                                | Qb[2:0] <sup>e</sup>                           |                      |     | 200                  |          |                             |

| t <sub>pw</sub>                | Output duty cycle                              | 45                   |     | 55                   | %        |                             |

| t <sub>jitter</sub>            | Cycle-to-cyle jitter, Standard deviation (RMS) |                      |     | 40                   | ps       | @f <sub>ref</sub> = 25MHz   |

| t <sub>lock</sub>              | Maximum PLL lock time                          |                      |     | 10                   | ms       |                             |

| t <sub>r</sub> /t <sub>f</sub> | Output Rise/Fall time                          | 50                   |     | 700                  | ps       |                             |

- c. Static phase offset between the selected reference clock and the feedback signal.

- d. Specification holds for a clock switch between two signals no greater than 400ps out of phase. Delta period change per cycle is averaged over the clock switch excursion. (See Applications Information section for more detail)

- e. Specification holds for a clock switch between two signals no greater than  $\pm\pi$  out of phase. Delta period change per cycle is averaged over the clock switch excursion.

- **f.** PECL output termination is 50 ohms to VCC 2.0V.

- g. V<sub>PP</sub> is the minimum differential input voltage swing required to maintain AC characteristic including SPO, device and part-to-part skew. Applicable to CLK0, CLK1 and Ext FB.

- h. V<sub>CMR</sub> is the crosspoint of the differential input signal. Normal operation is obtained when the crosspoint is within the V<sub>CMR</sub> range and the input swing lies within the V<sub>PP</sub> specification. Violation of V<sub>CMR</sub> or V<sub>PP</sub> impacts the SPO, device and part-to-part skew. Applicable to CLK0, CLK1 and Ext\_FB.

### **APPLICATIONS INFORMATION**

The XRK7933 is a dual clock PLL with on-chip Intelligent Dynamic Clock Switch circuitry.

#### **DEFINITIONS**

primary clock: The input CLK selected by Sel\_Clk.

secondary clock: The input CLK NOT selected by Sel\_Clk.

*PLL reference signal:* The CLK selected as the PLL reference signal by Sel\_Clk or the Intelligent Dynamic Clock Switch. The Intelligent Dynamic Clock Switch can override Sel\_Clk.

#### **STATUS FUNCTIONS**

Clk\_Selected: Clk\_Selected (L) indicates CLK0 is selected as the PLL reference signal. Clk\_Selected (H) indicates CLK1 is selected as the PLL reference signal.

Inp0bad, Inp1bad: Inp0bad is latched (H) when CLK0 is stuck (H) or (L) for at least one Ext\_FB period, or if one of the inputs CLK0 or CLK0 is floating. Inp1bad is latched (H) when CLK1 is stuck (H) or (L) for at least one Ext\_FB period, or if one of the inputs CLK1 or CLK1 is floating. Both Inp0bad and Inp1bad are latched (H) when Ext\_FB is stuck (H) or (L) for at least one Qa period, or if one of the inputs Ext\_FB or Ext\_FB is floating. Both Inp0bad and Inp1bad are cleared (L) on assertion of Alarm\_Reset. The status functions Inp0bad and Inp1bad are active for Man Override (H) or (L).

### **CONTROL FUNCTIONS**

Sel\_Clk: Sel\_Clk (L) selects CLK0 as the primary clock. Sel\_Clk (H) selects CLK1 as the primary clock.

*Alarm\_Reset:* Asserted by a negative edge. Generates a one–shot reset pulse that clears INPUT\_BAD latches and Clk\_Selected latch.

PLL\_En: While (L), the PLL reference signal is substituted for the VCO output.

MR: While (L), internal dividers are held in reset which holds all Q outputs LOW.

### MAN OVERRIDE (H)

(IDCS is disabled, PLL functions normally). PLL reference signal (as indicated by Clk\_Selected) will always be the CLK selected by Sel\_Clk. If Ext\_FB misses at least one pulse, Qa and Qb outputs will drop to a minimum frequency (~20MHz) for 1-uS, or until Ext\_FB shows any activity, whichever is longer. This prevents the Qa and Qb frequencies from rising due the PLL incorrectly interpreting an intermittent Ext\_FB as a VCO running too slow.

### MAN OVERRIDE (L)

Intelligent Dynamic Clock Switch is enabled. The first CLK to fail will latch it's INP\_BAD (H) status flag and select the other input as the Clk\_Selected for the PLL reference clock. Once latched, the Clk\_Selected and INP\_BAD remain latched until assertion of Alarm\_Reset which clears all latches (INP\_BADs are cleared and Clk Selected = Sel Clk).

If both Inp0bad and Inp1bad are (H), either due to both CLK0 and CLK1 having missed at least 1 pulse each or Ext\_FB having missed at least 1 pulse, then Qa and Qb outputs will drop to a minimum frequency (~20MHz) until such time as Alarm Reset b is asserted.

Note: If both CLKs are bad when Alarm\_Reset is asserted, both INP\_BADs will be latched (H) after one Ext\_FB period and Clk\_Selected will be latched (L) indicating CLK0 is the PLL reference signal. While neither INP\_BAD is latched (H), the Clk\_Selected can be freely changed with Sel\_Clk. Whenever a CLK switch occurs, (manually or by the Intelligent Dynamic Clock Switch), following the next negative edge of the newly selected PLL reference signal, the next positive edge pair of Ext\_FB and the newly selected PLL reference signal will slew to alignment.

To calculate the overall uncertainty between the input CLKs and the outputs from multiple XRK7933's, the following procedure should be used. Assuming that the input CLKs to all XRK7933's are exactly in phase, the total uncertainty will be the sum of the static phase offset, max I/O jitter, and output to output skew.

During a dynamic switch, the output phase between two devices may be increased for a short period of time. If the two input CLKs are 400ps out of phase, a dynamic switch of an XRK7933 will result in an instantaneous phase change of 400ps to the PLL reference signal without a corresponding change in the output phase (due to the limited response of the PLL). As a result, the I/O phase of a device, undergoing this switch, will initially

## **PRELIMINARY**

XRK7933

INTELLIGENT DYNAMIC CLOCK SWITCH PLL CLOCK DRIVER

be 400ps and diminish as the PLL slews to its new phase alignment. This transient timing issue should be considered when analyzing the overall skew budget of a system.

#### HOT INSERTION AND WITHDRAWAL

In PECL applications, a powered up driver will experience a low impedance path through an XRK7933 input to its powered down VCC pins. In this case, a 100 ohm series resistance should be used in front of the input pins to limit the driver current. The resistor will have minimal impact on the rise and fall times of the input signals.

## **ACQUIRING FREQUENCY LOCK**

- 1. While the XRK7933 is receiving a valid CLK signal, assert Man\_Override HIGH.

- 2. The PLL will phase and frequency lock within the specified lock time.

- 3. Apply a HIGH to LOW transition to Alarm\_Reset to reset Input Bad flags.

- 4. De-assert Man\_Override LOW to enable Intelligent Dynamic Clock Switch mode.

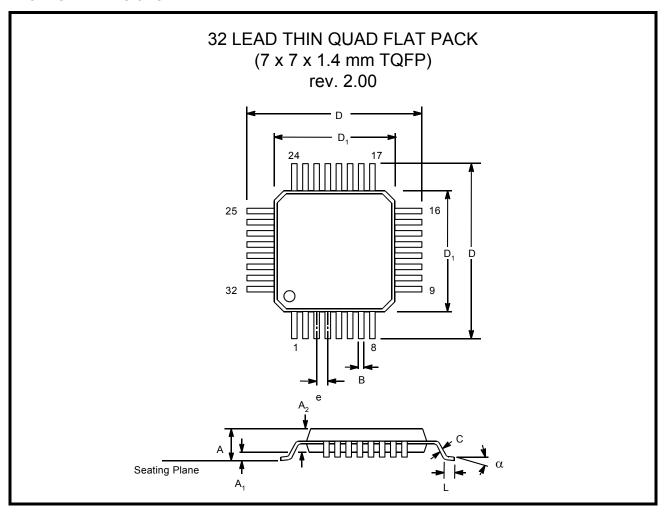

## **PACKAGE DIMENSIONS**

Note: The control dimension is the millimeter column

|                | INC        | HES   | MILLIN | IETERS     |

|----------------|------------|-------|--------|------------|

| SYMBOL         | MIN        | MAX   | MIN    | MAX        |

| Α              | 0.055      | 0.063 | 1.40   | 1.60       |

| A <sub>1</sub> | 0.002      | 0.006 | 0.05   | 0.15       |

| A <sub>2</sub> | 0.053      | 0.057 | 1.35   | 1.45       |

| В              | 0.012      | 0.018 | 0.30   | 0.45       |

| С              | 0.004      | 0.008 | 0.09   | 0.20       |

| D              | 0.346      | 0.362 | 8.80   | 9.20       |

| D <sub>1</sub> | 0.272      | 0.280 | 6.90   | 7.10       |

| е              | 0.0315 BSC |       | 0.80   | BSC        |

| L              | 0.018      | 0.030 | 0.45   | 0.75       |

| α              | 0°         | 7°    | 0°     | <b>7</b> ° |

#### **REVISION HISTORY**

| REVISION # | DATE         | DESCRIPTION                                                                      |

|------------|--------------|----------------------------------------------------------------------------------|

| A1.0.0     | August 2004  | Initial release.                                                                 |

| P1.0.0     | January 2005 | Revised Electrical characteristics, Application Section, changed to Preliminary. |

| P1.0.1     | March 2005   | Minor style edits.                                                               |

|            |              |                                                                                  |

|            |              |                                                                                  |

|            |              |                                                                                  |

|            |              |                                                                                  |

|            |              |                                                                                  |

|            |              |                                                                                  |

### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 2005 EXAR Corporation

Datasheet March 2005.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.